# Design considerations for CMOS low-noise amplifiers

|              | ence Paper - July 2004<br>09/RFIC.2004.1320538 · Source: IEEE Xplore                   |                |

|--------------|----------------------------------------------------------------------------------------|----------------|

| CITATION 138 | s s                                                                                    | READS<br>1,908 |

| 3 autho      | ors, including:                                                                        |                |

| 3            | Xiaoyong Li Shanghai Jiao Tong University 21 PUBLICATIONS 1,012 CITATIONS  SEE PROFILE |                |

| Some o       | f the authors of this publication are also working on these related projects:          |                |

| Project      | Low Noise Amplifier in CMOS View project                                               |                |

|              | Low Power Data Conversion Techniques View project                                      |                |

## Design Considerations for CMOS Low-Noise Amplifiers<sup>1</sup>

David J. Allstot, Xiaoyong Li, and Sudip Shekhar

Dept. of Electrical Engineering, Univ. of Washington, Seattle, WA 98195-2500

Abstract — A low-noise amplifier is the first active stage of a CMOS RF receiver. The inductively degenerated commonsource LNA (CS-LNA) topology is currently popular because it achieves high gain, low noise figure, etc. In this paper, its performance is reviewed and the optimum Q value that gives minimum noise figure is derived. It is then compared to the conventional common-gate LNA (CG-LNA) in terms of gain, noise figure, input matching, reverse isolation and stability. Finally, a general g<sub>m</sub>-boosted design technique for commongate RF circuits is introduced that provides lower noise figure and power consumption than the conventional CS-LNA and CG-LNA stages; it also preserves the CG-LNA insensitivity to parasitic input capacitances. In view of CMOS scaling, the CG-LNA topology is attractive for future higher frequency and/or lower power designs.

Index Terms — Low-noise amplifier, noise figure, RF receiver.

#### I. INTRODUCTION

Wireless communications systems demand high levels of integration, complex functionalities, and low cost implementations. After more than a decade of intensive research, CMOS has emerged as a viable technology for mixed-signal/RF system-on-chip solutions owing to the continued scaling of channel lengths; i.e., Moore's Law.

In an RF receiver, the input signal from an antenna first passes through an LNA that amplifies it and suppresses noise contributions from subsequent stages [1]. Hence, low noise figure and high gain are critical LNA performance parameters; in portable applications, low power dissipation is also essential. LNA design involves tradeoffs among linearity, input matching, power dissipation, etc.

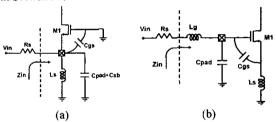

The basic common-source and common-gate LNA circuits depicted in Fig. 1 are widely used in CMOS RF IC design. The CS-LNA configuration is currently popular because of its superior noise performance; i.e., the inductive degeneration is ideally noiseless and the RF input signal is pre-amplified by the input-matching series resonant network. In contrast, the CG-LNA topology provides a wideband input match that is less sensitive to input parasitic capacitances (e.g., bond pad, etc.) [2].

In this paper, a general g<sub>m</sub>-boosted design technique for common-gate RF circuits is presented. Implemented using cross-coupled capacitors, a fully differential g<sub>m</sub>-boosted

CG-LNA exhibits superior performance to its conventional common-gate counterpart and outperforms the CS-LNA configuration at higher RF frequencies. (Note: Although not described herein, implementations of the g<sub>m</sub>-boosted technique are also possible using other passive coupling networks such as inductors, etc.) The paper is organized as follows: Section II compares the basic CS-LNA and CG-LNA topologies in terms of gain, noise figure, input matching accuracy, etc. Section III describes the general g<sub>m</sub>-boosted technique and presents results that confirm its advantages. Conclusions are given in Section IV.

Fig. 1. Basic low-noise amplifier topologies: (a) Common-gate (CG-LNA), and (b) common-source (CS-LNA).

## II. CMOS LNA TOPOLOGIES

A task in LNA design is to create a  $50\Omega$  resistive input impedance as required by the preceding band-select filter. Its key specifications including insertion loss, pass band ripple, stop band attenuation, etc., are guaranteed to be met only over a specified range of terminating impedances; e.g., between  $25\Omega$  and  $100\Omega$ . Terminating impedances outside this range result in substantial performance degradations. The LNA should also be designed so that it adds minimum noise in the RF signal path while synthesizing the input impedance of  $50\Omega$ . This precludes obvious approaches such as shunting a  $50\Omega$  resistor at the input to create the termination impedance. Next, performance characteristics of the basic CS-LNA and CG-LNA topologies are analyzed and compared.

### A. Input Matching

The input impedance  $(50\Omega)$  of the CG-LNA stage (Fig. 1(a)) is approximately  $1/g_{m1}$  of input MOSFET  $M_1$ , while that of the CS-LNA circuit (Fig. 1(b)) is [3]:

<sup>&</sup>lt;sup>1</sup> Research supported by National Science Foundation contracts CCR-0086032 and CCR-0120255 and Semiconductor Research Corporation contracts 2001-HJ-926 and 2003-TJ-1093.

$$Z_{in} = s(L_g + L_s) + \frac{1}{sC_{gs}} + \left(\frac{g_{mt}}{C_{gs}}\right)L_s$$

$$\approx s(L_g + L_s) + \frac{1}{sC_{gs}} + \omega_T L_s$$

$Z_{in}$  is specified by choosing  $L_{g}$  and  $L_{s}$  to resonate with  $C_{gs}$  at the operating frequency with  $(g_{m1}/C_{gs})L_{s}$  set to 50 $\Omega$ .

A fundamental difference between the input matching networks is that CS-LNA is series resonant while CG-LNA is parallel resonant; the associated quality factors are

$$Q_{CS-LNA} = \frac{1}{2\omega_0 C_{gs} R_s} > 1 \leftrightarrow Q_{CG-LNA} = \frac{\omega_0 C_{gs} R_s}{2} < 1$$

It is known that the sensitivity of  $Z_{in}$  to parasitic components is proportional to the quality factor of the matching network [4]. Hence, CG-LNA with its lower Q parallel resonant network is more robust against typical production process, voltage, and temperature variations. Moreover, parasitic capacitance at the CG-LNA input is naturally absorbed into the LC tank (Fig. 1(a)).

#### B. Gain

The effective transconductance of the CS-LNA stage is

$$G_{m,CS-I,NA} = g_{m1}Q = \frac{g_{m1}}{\omega_0 C_{gs} (R_S + \omega_T L_s)} = \frac{\omega_T}{\omega_0 R_S \left(1 + \frac{\omega_T L_s}{R_S}\right)}$$

With the input matched to  $R_{\rm S}$ ,

$$G_{m,CS-LNA} = \frac{1}{2Rs} \left( \frac{\omega_T}{\omega_0} \right)$$

In RF systems  $R_S$  is usually equal to  $50\Omega$ . Note that  $G_m$  depends only on the ratio of  $\omega_T$  to  $\omega_D$  and is independent of the MOSFET small-signal transconductance  $g_{m1}$ . In contrast, the effective input transconductance of CG-LNA under perfect input matching conditions is

$$G_{m,CG-LNA} = \frac{1}{2}g_{m1} = \frac{1}{2Rs}$$

The value of  $\omega_1/\omega_0$  typically lies in the range of 5~10, depending on the operating frequency and process details. Therefore, CS-LNA provides higher gain than its conventional common-gate counterpart.

## C. Noise Figure

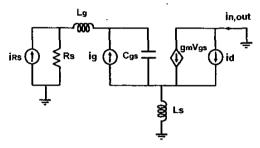

A major advantage of the common-source amplifier with inductive degeneration is that the resistive input impedance is noiseless, unlike other topologies where a noisy resistor is added in the signal path to create a  $50\Omega$  terminating impedance. Figure 2 depicts a small-signal circuit for noise analysis of CS-LNA with inductive degeneration. The noise factor of this topology is

$$F = \frac{\overline{i_{n,out}^2}}{\overline{i_{Ry}^2}} = 1 + \frac{\gamma}{\alpha} \frac{1}{Q} \left(\frac{\omega_0}{\omega_T}\right) \left[1 + \frac{\delta \alpha^2}{5\gamma} (1 + Q^2) + 2|c| \sqrt{\frac{\delta \alpha^2}{5\gamma}}\right]$$

(1)

$$\frac{\overrightarrow{i_{Rs}}}{\overrightarrow{i_{R}}} = \frac{4kT\Delta f}{R_s}$$

$$\frac{\overrightarrow{i_d}}{\overrightarrow{i_g}} = 4kT\gamma g_{d0}\Delta f$$

$$\overrightarrow{i_g} = 4kT\delta g_g\Delta f$$

$$Q = \frac{1}{a_0 C_{gs}R_s}$$

$$\overrightarrow{i_g i_d} = c\sqrt{\overrightarrow{i_g i_d}}$$

where c = j0.395,  $\alpha$ ,  $\gamma$ , and  $\delta$  are bias-dependent parameters [5], and  $\omega_0$  and  $\omega_T$  are the operating and unity current gain frequencies, respectively.

Fig. 2. Small-signal circuit for noise figure analysis of CS-LNA.

The results above reveal the impact of Q on noise figure in CS-LNA. From (1), noise in CS-LNA comprises three factors: channel noise, gate noise and correlated noise. Increasing Q of the input resonant circuit reduces the contribution of channel noise. In contrast, gate noise is enhanced by the Q factor. Hence, there exists an optimum Q that minimizes the noise figure. For a given overdrive voltage and  $f_T$ , the optimum values are

$$F_{\min,CS-LNA} = 1 + \frac{\gamma}{\alpha} \left( \frac{\omega_0}{\omega_T} \right) \frac{2\delta\alpha^2}{5\gamma} Q_{opt}$$

$$Q_{opt} = \sqrt{1 + 2|c| \sqrt{\frac{5\gamma}{\delta\alpha^2}} + \frac{5\gamma}{\delta\alpha^2}}$$

(2)

To achieve a high  $f_T$ , minimum channel length is used. Knowing the optimum Q value for minimum noise figure, the optimum width of the device is then easily determined.

For CG-LNA, the noise factor is approximately constant with respect to the operating frequency,

$$F_{CG-LNA} = 1 + \frac{\gamma}{\alpha}$$

The noise factor of CG-LNA is constant with respect to  $\omega_0/\omega_T$ , while that of CS-LNA is linear with  $\omega_0/\omega_T$ .

#### D. Reverse Isolation and Stability

In a conventional CS-LNA,  $C_{gd}$  provides a feed-forward path between input and output that degrades reverse isolation and stability. In contrast, since the Miller effect on  $C_{gd}$  does not exist in CG-LNA; it exhibits better reverse isolation and stability. Also, cascoding is not necessary in

conventional CG-LNA so there is no added noise from cascode transistors.

In summary, CG-LNA achieves better input matching, reverse isolation and stability than CS-LNA. However, the higher noise figure has impeded its use for low noise amplification. In the next section, it is shown that the gmboosted technique is advantageous in common-gate amplifiers to achieve a lower noise figure, especially at higher frequencies, while consuming less power.

### III, G,-BOOSTED CG-LNA TOPOLOGY

Since noise figure is the most important characteristic of an LNA, the noise calculations of the CG-LNA stage are briefly revisited. It can be shown that the noise factor is

$$F_{CG-LNA} = 1 + \frac{\gamma}{\alpha} \frac{1}{g_{m1} R_S}$$

(3)

where induced gate noise is negligibly small.

As (3) implies, increasing  $g_{m1}$  reduces the noise factor. In RF systems, however, input matching requires that  $g_{m1} = 1/R_S$ , which results in  $F = 1+\gamma/\alpha$ . From another point of view, it is the input-matching requirement that prevents increasing  $g_{m1}$  to lower the noise factor, and this in turn sets a lower bound on the noise factor. Note that in CG-LNA, impedance matching may be traded against noise figure. More specifically, if some input mismatch can be tolerated,  $g_{m1}$  can be increased to decrease the noise figure while the input reflection is maintained below some reasonable value [2]. For example, if  $\gamma = 2$  and  $1/g_{m1} = 30\Omega$ ,  $S_{11} = -12dB$ , which is often acceptable. In this case, NF = 3.4dB, which is about 1.4dB lower than the value of 4.8dB when the input is matched to  $50\Omega$ .

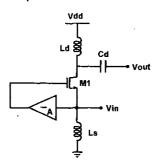

Fig. 3. G<sub>m</sub>-boosted common-gate LNA.

The discussion above illuminates the tight link between noise figure and input matching in CG-LNA. If the condition of input matching can be separated from noise performance, the possibility of improving noise figure arises. The proposed scheme is based on an important observation: two  $g_m$  values are used in calculating the noise factor of the common-gate amplifier. One is the

effective transconductance looking into the source terminal; denote it as  $G_m$ . The other is the intrinsic transconductance of the amplifying device, which is related to drain current channel noise  $i_d$  and is denoted as  $g_{m1}$ . In general,  $G_m$  is not necessarily equal to  $g_{m1}$ . However, in a conventional CG-LNA in which the gate terminal is shorted to ac ground,  $G_m = g_{m1}$ . A design challenge in improving CG-LNA is to modify the topology so that  $G_m \neq g_{m1}$ . Specifically, to make  $G_m \neq g_{m1}$ , a coupling mechanism is introduced between the gate and source terminals.

Figure 3 depicts the topology of the proposed  $g_m$ -boosted CG-LNA. In this structure, rather than connecting the gate terminal to a dc bias voltage, an inverting amplification is introduced between the source and gate nodes of the MOSFET. Consequently, the effective transconductance looking into the source terminal is boosted from  $G_m = g_{m1}$  to  $G_m = (1+A)g_{m1}$ , where A is the gain from source to gate. Most important, the resulting noise factor becomes

$$F_{CG-LNA,GM-BOOSTED} = 1 + \frac{\gamma}{\alpha} \frac{1}{(1+A)^2 g_{ml} Rs}$$

Input matching requires that  $(1+A)g_{m1} = 1/R_S$  resulting in

$$F_{CG-INA,GM-BOOSTED} = 1 + \frac{\gamma}{\alpha} \frac{1}{1+A}$$

It is clear that the noise factor of the structure shown in Fig. 3 is reduced by the factor (1+A). For example, if A=1,  $\gamma=2$ ,  $\delta=4$ ,  $\alpha=0.85$ , then

$$NF_{CG-LNA} = 5.25dB \leftrightarrow NF_{CG-LNA,CM-BOOSTED} = 3.38dB$$

It can be seen that 1.9dB of improvement in the noise figure is achieved by the g<sub>m</sub>-boosted CG-LNA relative to its conventional counterpart.

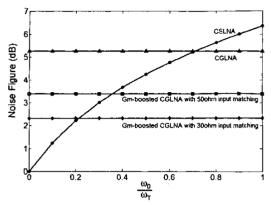

Figure 4 compares noise figures of various LNA circuits. The  $g_m$ -boosted CG-LNA (with A=1) achieves lower noise figure than CS-LNA for  $\omega_0/\omega_T>0.35$ . In addition, if  $1/g_m=30\Omega$ ,  $S_{11}=-12dB$ , which is usually an acceptable value, the  $g_m$ -boosted CG-LNA outperforms CS-LNA for  $\omega_0/\omega_T>0.2$ . It also consumes less power than the conventional CG-LNA. That is, since  $(1+A)g_{m,new}=1/R_S$ ,  $g_{m,new}$  is reduced to  $1/(1+A)g_m$  and the power consumption is reduced by the same factor. The  $g_m$ -boosted CG-LNA is attractive for high frequency applications.

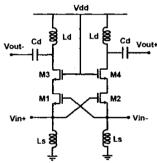

Next, capacitor cross-coupled CG-LNA [6] is reviewed as one possible implementation of a  $g_m$ -boosted CG-LNA. As shown in Fig. 3, an inverting amplification is required between the source and gate terminals. In differential circuits, the inverting gain is naturally available (with A = 1) as shown in Fig. 5 wherein  $L_s$  resonates with the input

node capacitance at the operating frequency.  $L_d$  and  $C_d$  form an L-match circuit at the output. However, unlike in conventional CG-LNA,  $C_{gd}$  in Fig. 5 experiences the Miller effect, which degrades the reverse isolation. Cascodes  $(M_3$  and  $M_4)$  are added to improve reverse isolation and stability.

Fig. 4. Noise figure of the CS-LNA, CG-LNA and  $g_m$ -boosted CG-LNA stages versus  $\omega_0/\omega_T$ .

Fig. 5. Capacitor cross-coupled common-gate LNA [6].

The circuit of Fig. 5 is simulated in SPECTRE-RF at 5.6GHz. The simulations are performed using a 1.8V, 180nm CMOS technology. For comparison, the conventional CS-LNA and CG-LNA shown in Fig. 1 are also designed and simulated using the same process. Table I compares the performance of conventional CS-LNA, CG-LNA and capacitive cross-coupling CG-LNA circuits. Simulation results show that the capacitive cross-coupling CG-LNA circuit achieves a lower noise figure and consumes less dc power. Furthermore, the calculated noise figure for the capacitor cross-coupled CG-LNA based on the analysis described above for g<sub>m</sub>-boosted CG-LNA agrees closely with the simulated results.

Table I. LNA Performance Comparison

|                                  | CS-LNA | CG-LNA | Gm-Boosted<br>CG-LNA |

|----------------------------------|--------|--------|----------------------|

| Frequency (GHz)                  | 5.6    | 5.6    | 5.6                  |

| S11 (dB)                         | -28.1  | -39.6  | -16.4                |

| S21 (dB)                         | 16.2   | 9.0    | 10.4                 |

| S12 (dB)                         | -28.3  | -40.7  | -44.3                |

| S22 (dB)                         | -23.4  | -25.6  | -26.4                |

| NF (dB)                          | 2.87   | 2.95   | 1.69                 |

| NF with M <sub>1</sub> only (dB) | 2.26   | 2.10   | 1.00                 |

| Calculated NF (dB)               | NA     | 2.08   | 0.95                 |

| IIP3 (dBm)                       | -5.1   | 3.64   | 2.96                 |

| DC Current (mA)                  | 6.2    | 2.65   | 1.80×2               |

#### IV. CONCLUSIONS

A general g<sub>m</sub>-boosted CG-LNA topology is detailed that exhibits lower noise figure and consumes less power than conventional CG-LNA. It also preserves the advantages of insensitivity to parasitic input capacitance, higher reverse isolation and better stability, which makes it attractive for emerging high frequency applications. Implementation of the g<sub>m</sub>-boosted CG-LNA scheme is also discussed and simulations show good agreement between analysis and simulated results. The g<sub>m</sub>-boosted topology provides new opportunities for circuit innovation; implementations using other coupling techniques are under development.

#### REFERENCES

- D.J. Allstot, "Low Noise Amplifiers," IEEE International Solid-State Circuits Conference Short Course, 2001.

- [2] H. Darabi, et al., "A 4.5-mW 900-MHz CMOS receiver for wireless paging," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1085-1096, Aug. 1997.

- [3] D.K. Shaeffer, et al., "A 1.5-V, 1.5-GHz CMOS low-noise amplifier," *IEEE J. Solid-State Circuits*, vol. 32, pp. 745-759, May 1997.

- [4] Q. Huang, et al., "The impact of scaling down to deep submicron on CMOS RF circuits," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1023-1036, July 1998.

- [5] Y. Cheng, et al., "High-frequency small-signal ac and noise modeling of MOSFETs for RF IC design," *IEEE Trans. Electron Devices*, vol. 49, pp. 400-408, March 2002.

- [6] W. Zhuo, et al., "Using capacitive cross-coupling technique in RF low noise amplifiers and down-conversion mixer design," ESSCIRC Digest, pp. 116-119, Sept. 2000.

#### 29.3 Low-Power g<sub>m</sub>-boosted LNA and VCO Circuits in 0.18µm CMOS

Xiaoyong Li, Sudip Shekhar, David J. Allstot

University of Washington, Seattle, WA

As multi-channel transceivers emerge, there is a growing demand for CMOS RF front-end circuits that give state-of-the-art performance, consume less power, and exhibit robustness against PVT variations. Previously, the inductively degenerated commonsource LNA (CSLNA) and the cross-coupled LC VCO topologies were dominant. We propose the passively-coupled common-gate LNA (CGLNA) and Colpitts VCO configurations as alternatives. A CGLNA, a differential Colpitts VCO, and a quadrature VCO (QVCO) are presented that employ  $g_m$ -boosting with low current

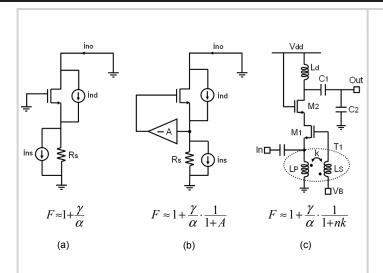

A conventional CGLNA (Fig. 29.3.1a) has superior input matching, linearity, stability and robustness to PVT variations [1], but the inductively degenerated CSLNA achieves a lower noise figure (NF) at low operating frequencies. The input matching requirement of  $g_{\rm m}R_{\rm s}=1$  for CGLNA bounds its noise factor at  $F=1+\gamma/\alpha$ where  $\alpha = g_m/g_{d0}$ . Clearly,  $\alpha$  should be increased to decrease F. This seems infeasible because  $\alpha$  is constrained at the device level. However, passive coupling techniques proposed herein allow the effective  $g_m$  to be increased without increasing  $g_{d0}$ . Figure 29.3.1b depicts the  $g_m$ -boosted scheme where an inverting gain from source to gate decouples  $g_m$  from  $g_{d0}$ . The effective transconductance at the input is increased to  $(1+A)g_m$  and F is reduced to  $1+\gamma/(1+A)\alpha$ .

Noise issues prohibit active realizations of the inverting gain A. One possible passive implementation employs capacitor crosscoupling using inversions available in a differential topology [2]. However, a differential configuration consumes 2X more current and silicon area than a single-ended version, and the gate capacitance makes A < 1.

To minimize current consumption and realize  $A \ge 1$ , an on-chip transformer is used to achieve anti-phase operation between the source and gate terminals of  $M_1$  (Fig. 29.3.1c).  $A = kn = k\sqrt{L_S/L_p}$  is determined by the turns ratio n and the coupling factor k of transformer  $T_1$ . The small-signal input admittance at the source is  $Y_{in} \approx 1/sL_p + (1+kn)g_m + (1+2kn+n^2)sC_{gs}$ . Assuming ideal magnetic coupling (k=1) and n=1:1,  $Y_{in} \approx 1/sL_p + 2g_m + 4sC_{gs}$ . Thus, the use of transformer coupling effectively doubles the transconductance and enables a 2X reduction in power consumption. In addition, F is reduced to  $1+\gamma/2\alpha$  under the new input matching condition  $2g_mR_s=1$ .

LNA and VCO circuits share many similarities. For example, a Colpitts oscillator can be viewed as a common-gate amplifier in a positive feedback configuration. Its phase noise is superior to a cross-coupled VCO [3] because the noise current from active devices is injected into the LC tank when the tank voltage is minimum and the impulse sensitivity is low. However, poor start-up characteristics, high power consumption, lower tuning range and lack of differential operation have impeded its adoption. The design presented in [3] addresses these shortcomings through the use of a current-switching technique. We use the common-gate  $g_m$ -boosting techniques to overcome these drawbacks.

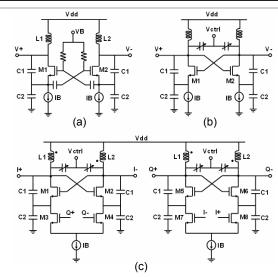

In order to realize a differential Colpitts oscillator with enhanced transconductance, the gate of one branch is connected to a node with an opposite voltage swing to that of the source. As depicted in Fig. 29.3.2a, the two branches can be capacitive cross-coupled. The resultant increase in transconductance eases the start-up requirement with lower power consumption than other techniques. The in-phase relationship between the source and drain voltages (via capacitive feedback with  $C_1$  and  $C_2$ ) also suggests an

alternative approach - to connect the gate to the drain of the other branch, resulting in the self-biased Colpitts configuration (Figure 29.3.2b). This topology has an effective transconductance of  $-(2C_1C_2+C_2^2)g_m/(C_1+C_2)^2$ , which is  $(2+C_2/C_1)$  times higher than that of the standard Colpitts VCO. Furthermore, because the gate and source terminals are driven with anti-phase signals, faster commutation with better noise suppression from the differential pair is achieved.

In a standard cross-coupled VCO, the second harmonic present at the common-source node is modulated by the flicker noise from the differential pair and down-converted to the fundamental frequency, thus increasing the close-in phase noise [4]. This phenomenon does not arise in the proposed differential Colpitts topologies because there is no common-source node present, which leads to a superior close-in phase noise performance.

Finally, applying series coupling [4] to the VCO of Fig. 29.3.2b leads to the Colpitts QVCO of Fig. 29.3.2c. Optimization of the QVCO involves sizing both the switching and coupling transistors to achieve efficient current switching with minimal phase noise. On-chip transformers are used to avoid long interconnect lines and to obtain higher Q (≈10) than with the inductors (Q≈8) used in the VCO. Active tail current sources are used rather than resistors in the VCO/QVCO for better robustness at the expense of higher flicker noise.

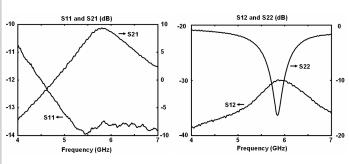

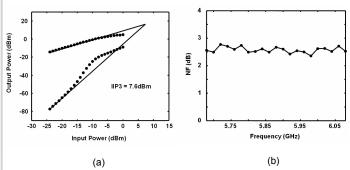

A prototype chip is fabricated in a standard 6-metal 0.18µm CMOS RF process. For the  $g_m$ -boosted CGLNA, a transformer turns ratio of 1:1 is chosen for demonstration purposes. Further reduction in NF is possible with A>1 using a larger turns ratio. The measured S-parameters (Fig. 29.3.3) show  $S_{21}$  of 9.4dB peaking at 5.8GHz. The LNA draws only 1.9mA from 1.8V owing to the g<sub>m</sub>-boosting technique. Measured IIP3 is 7.6dBm and NF at maximum gain is 2.5dB (Fig. 29.3.4). The proposed LNA has an excellent FOM compared to competing designs (Fig. 29.3.6). It is noted that some common-source designs achieve better noise performance at higher power consumption and with off-chip compo-

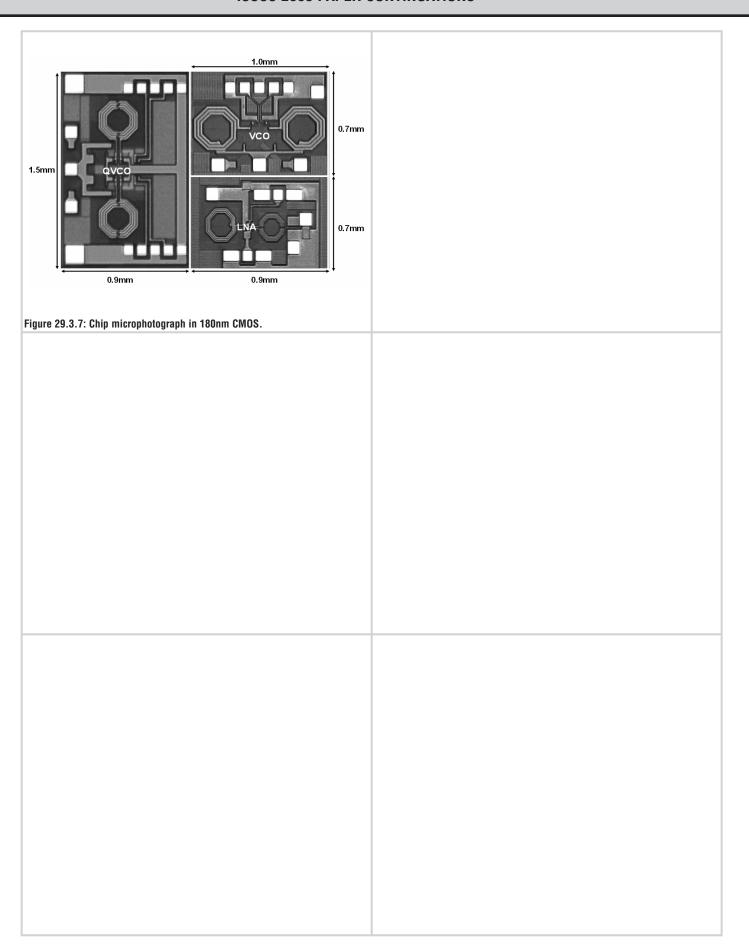

The Colpitts differential VCO (Fig. 29.3.2b) operates at a center frequency of 1.79GHz with a tuning range of 22% while the Colpitts QVCO (Fig. 29.3.2c) operates from 1.83GHz to 2.24GHz for a 20% tuning range. Figure 29.3.5 shows measured phase noise plots of the VCO/QVCO. The VCO has a phase noise of -97dBc/Hz at 50kHz offset and -128dBc/Hz at 1MHz offset. It draws 3.6mA from a 2.0V supply. The QVCO draws only 4.3mA from 2.0V to attain a close-in phase noise of -104dBc/Hz at 50kHz offset. Its phase noise at 1MHz offset is -127dBc/Hz. Figure 29.3.6 compares its FOM to existing designs. The chip micrograph is shown in Fig. 29.3.7.

#### Acknowledgements:

This work was supported by the Air Force Research Laboratory, Space Vehicles Directorate, Kirtland AFB, NM under contract F29601-02-2-0299, entitled "Mixed-Signal Electronics Technology for Space", and by NSF contract CCR-0086032 and SRC contract 2003-TJ-1093

#### References:

[1] D. Allstot et al., "Design Considerations for CMOS Low-Noise

Amplifiers," *RFIC*, pp. 97-100, 2004.

[2] W. Zhuo et al., "Using Capacitive Cross-coupling Technique in Low-Noise Amplifiers and Down-Conversion Mixer Design," ESSCIRC, pp. 116-

[3] R. Aparicio et al., "A CMOS Differential Noise-shifting Colpitts VCO," ISSCC Dig. Tech. Papers, pp. 288-289, Feb., 2002.

[4] A. Ismail et al., "CMOS Differential LC Oscillator with Suppressed Up-Converted Flicker Noise," ISSCC Dig. Tech. Papers, pp. 98-99, Feb., 2003.

[5] P. Andreani, "A 2GHz 17% Tuning Range Quadrature CMOS VCO with High Figure-of-Merit and 0.6° Phase Error," ESSCIRC, pp. 815-818, 2002.

Figure 29.3.1: (a) Conventional CGLNA;  $g_{\rm m}\text{-boosted}$  CGLNA with (b) active, and (c) transformer coupling.

Figure 29.3.2: Evolution of  $g_m$ -boosted Colpitts oscillators. (a) Capacitor-coupled VCO with separate gate bias, (b) self-biased VCO, and (c) self-biased QVCO.

Figure 29.3.3: Measured LNA S-parameters.

Figure 29.3.4: Measured LNA (a) IIP3, and (b) Noise Figure.

| -80                          |                       |     |                      | -90        | che re                                 | Ш              | Ш    |   | Ш     |    |   |     |    |

|------------------------------|-----------------------|-----|----------------------|------------|----------------------------------------|----------------|------|---|-------|----|---|-----|----|

| -90                          | Na Piku.              |     |                      | -100       | LANGE OF THE                           |                | ₩    | + | Ш     |    | + | Н   | Щ  |

| -100<br>-110<br>-120<br>-130 |                       |     | Phase Noise (dBc/Hz) | -110       |                                        | 1774           |      |   |       |    |   |     |    |

| -120                         | 177                   |     | Noise                | -120       |                                        | $\blacksquare$ |      | 1 |       |    | 4 | H   |    |

| -130<br>-140                 |                       | 100 | Phas                 | -130       |                                        |                |      |   | - 179 |    | 4 | No. |    |

| -150<br>10K                  | 100K                  | 1M  | 10M                  | -140<br>10 | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | Щ              | 100K |   | Щ     | IM |   | 77  | 10 |

| 1010                         | Offset Frequency [Hz] |     |                      |            |                                        |                | 10   |   |       |    |   |     |    |

|                              | (b)                   |     |                      |            |                                        |                |      |   |       |    |   |     |    |

Figure 29.3.5: Measured phase noise of (a) VCO, and (b) QVCO.

| Ref. LNA              | CMOS Tech.<br>(nm) | Freq.<br>(GHz) | Power<br>(mW) | NF<br>(dB) | S21<br>(dB) | IIP3<br>(dBm)        | Fully<br>on-chip | $FOM = \frac{Gain_{abs} \cdot IIP3_{mW}}{(F-1)P_{mW}}$                              |               |  |

|-----------------------|--------------------|----------------|---------------|------------|-------------|----------------------|------------------|-------------------------------------------------------------------------------------|---------------|--|

| This work             | 180                | 5.8            | 3.4           | 2.5        | 9.4         | 7.6                  | Yes              |                                                                                     | 37.0          |  |

| Fujimoto<br>JSSC02    | 250                | 7              | 13.8          | 3.3        | 6.2         | 8.4                  | Yes              |                                                                                     | 6.3           |  |

| Steyaert<br>ISSCC02   | 250                | 1.57           | 8             | 1.5        | 15.5        | -6.0                 | Yes              |                                                                                     | 0.7           |  |

| Youn<br>ISSCC03       | 250                | 2.2            | 2X11.8        | 3          | 14.9        | 16.1                 | Yes              | 21.3 (0                                                                             | lifferential) |  |

| Cha<br>JSSC03         | 350                | 5.2            | 26.4          | 2.45       | 19.3        | -6.1                 | No               |                                                                                     | 0.6           |  |

| Cassan<br>JSSC03      | 180                | 5.75           | 2X8           | 0.9        | 14.2        | 0.9                  | No               | 9.85 (0                                                                             | lifferential) |  |

| Ref. QVCO             | смоѕ               | Freq.          | Power         | Tuning     | Tank        | Phase Noise (dBc/Hz) |                  | $FOM = 10 \cdot \log_{10} \left( f_0 / Af \right)^2 / L \left\{ Af \right\} P_{at}$ |               |  |

|                       | Tech.<br>(nm)      | (GHz)          | (mW)          | Range      | Q           | @50KHz               | @1MHz            | @50KHz                                                                              | @1MHz         |  |

| This work             | 180                | 1.83           | 8.6           | 20%        | 10          | -104                 | -127             | 185.9                                                                               | 182.9         |  |

| Kim<br>JSSC02         | 180                | 1.1            | 5.4           | 28%        | NA          | -95                  | -120             | 174.5                                                                               | 173.5         |  |

| Steyaert<br>JSSC02    | 250                | 1.57           | 30            | 24%        | 20          | -108                 | -138             | 183.2                                                                               | 187.1         |  |

| Tiebout<br>JSSC01     | 250                | 1.8            | 20            | 17%        | 8           | -105                 | -136             | 183.1                                                                               | 188.1         |  |

| Andreani<br>ISSCC02   | 350                | 1.8            | 50            | 18%        | 6           | -98                  | -133             | 172.1                                                                               | 181.1         |  |

| Andreani<br>ESSCIRC02 | 350                | 2              | 20.8          | 17%        | 6           | -98                  | -130             | 176.9                                                                               | 182.8         |  |

Figure 29.3.6: LNA and QVCO performance comparisons.

Continued on Page 615

## **ISSCC 2005 PAPER CONTINUATIONS**